Chapter 2. The processor

36

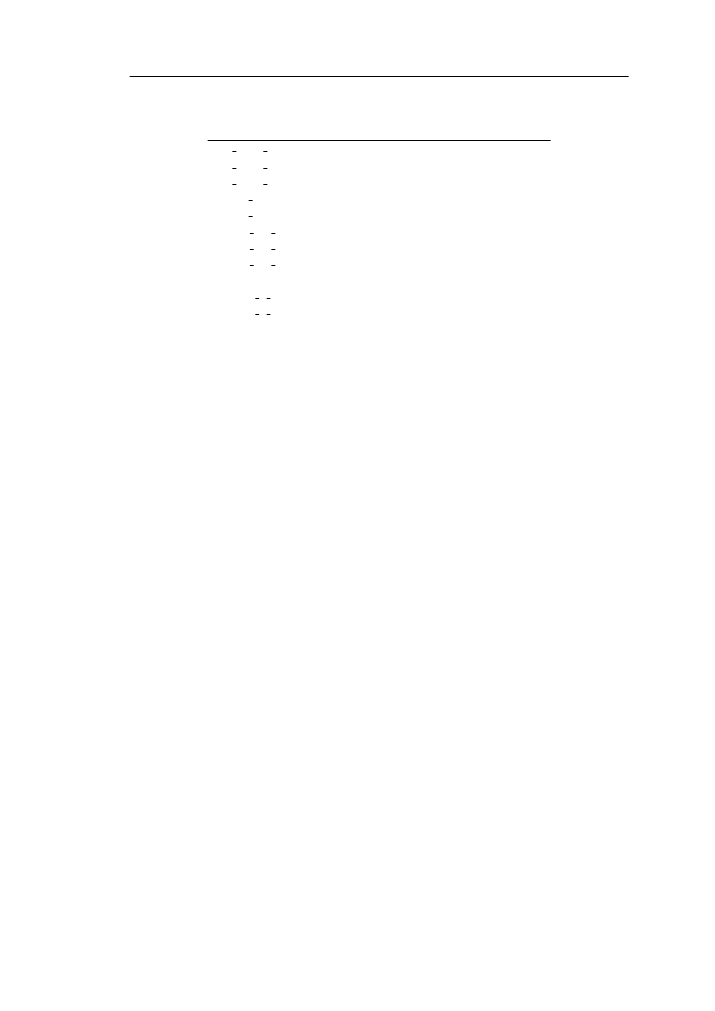

Table 2.15: The Bypassing unit

Name

Type

Size

Explanation

Rd addr stg3

input signal

5

stage 3 Rd address

Rd addr stg4

input signal

5

stage 4 Rd address

Rd addr stg5

input signal

5

stage 5 Rd address

Rs1 addr

input signal

5

Rs1 read address

Rs2 addr

input signal

5

Rs2 read address

pred stg 3

input signal

1

stage 3 pred signal

pred stg 4

input signal

1

stage 4 pred signal

pred stg 5

input signal

1

stage 5 pred signal

op

input signal

6

operation

mux 3 s

output signal

3

M3 signals

mux 4 s

output signal

3

M4 signals

Several other solutions could be applied to solve the problems of the multi-cycle instruc-

tions, such as out-of-order-execution parallel module operation, where other units can

operate while others are busy, and scoreboarding, but this requires a lot of research and

experimentation which would be off the limits of this thesis work.

2.10.5

Register Forwading

Another solution which is extensively used in the processor is data forwarding. Forward-

ing involves feeding output data into a previous stage of the pipeline to avoid the reading

of corrupt data. This is achieved by having the control unit constantly monitoring all

the stages and the register data used by those stages. If one stage has available data that

is required by another stage then those data are forwarded to this stage. For example

in table

the way to deal with the hazard that occurs in T3 is to forward the value

of the R28 at stage 3 back to stage 2. This is achieved by a simple multiplexor which

drives the proper data.

In this implementation there is data forwarding from stages 3,4,5 back to stage 2. The

control unit monitors from every stage the instruction, the read and write registers, as

well as the predicate of each instruction and with a simple combinational logic forwards

the proper data through the multiplexors M3 and M4. Table

displays the ports

used by the bypassing unit.