Chapter 2. The processor

34

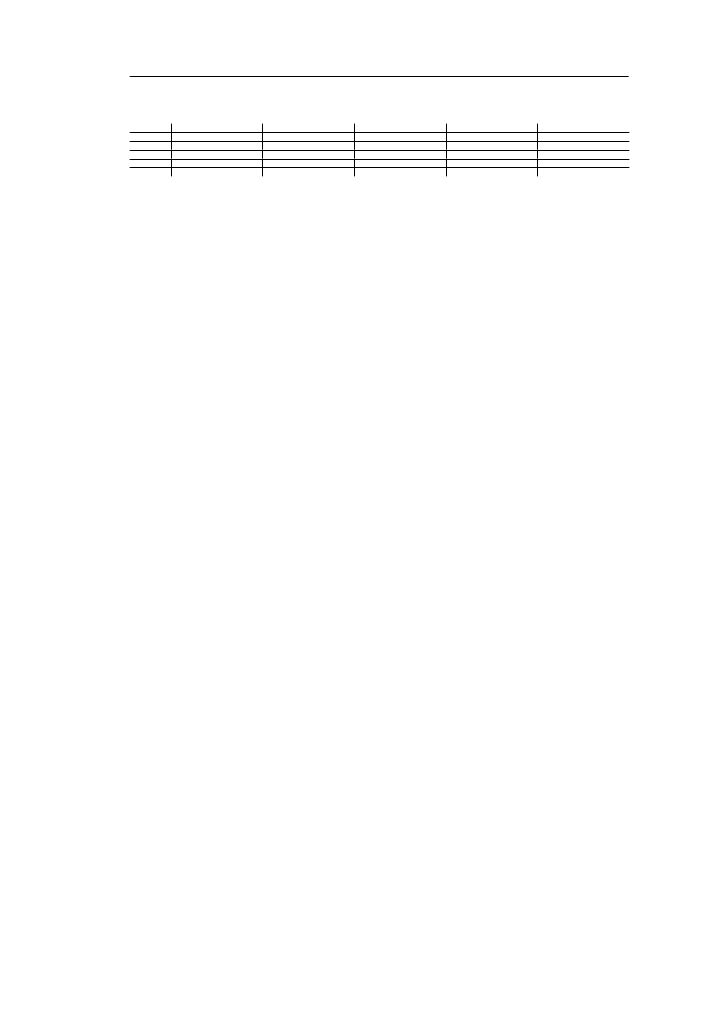

Table 2.13: Read after write hazard example

T1

T2

T3

T4

T5

stage 1

add(R28, R21, R23)

add(R20, R28, R21)

stage 2

add(R28, R21, R23)

add(R20,

R28

, R21)

stage 3

add(

R28

, R21, R23)

add(R20, R28, R21)

stage 4

add(R28, R21, R23)

add(R20, R28, R21)

stage 5

add(R28, R21, R23)

2.10

Hazards and data corruption

While the pipeline implementation boosts the performance the main drawback is the

hazards that can occur while the execution takes place. Instructions in a pipelined

processor are performed in several stages, so that at any given time several instructions

are being processed in the various stages of the pipeline, such as fetch and execute.

There are many different instruction pipeline micro-architectures, and instructions may

be executed out-of-order. A hazard occurs when two or more of these simultaneous

(possibly out of order) instructions conflict.

2.10.1

Read after write hazard

A read after write hazard occurs when an instruction tries to read a result that has

not yet been calculated and therefore reads corrupt data. This occurs because even

though the instruction is executed after the previous instruction the result has not yet

fully propagated through the pipeline. If for example in our implementation an add

operation is being executed in the third stage, the actual register update will take place

after two cycles in the fifth stage. As a result any data read that occurs in the second

stage that targets the same register as the one that is bound to be updated in stage 3,

will receive corrupt data. In table

an example of such hazard is displayed. While

the first add instruction is in the third stage of the pipeline, it still has not updated the

R28 register. However at the same T3 time the next add instruction is already reading

the R28 register which has corrupt data.

2.10.2

Branch Hazards

Despite the fact that using the predicate system eliminates the branch prediction haz-

ards, there is one exception. This hazard can occur with the ”jump” instruction. Since

all instructions are predicated so is the ”jmp” instruction, if there is a compare instruc-

tion to be executed in the pipeline(which is responsible for updating the predicate file)