Chapter 2. The processor

24

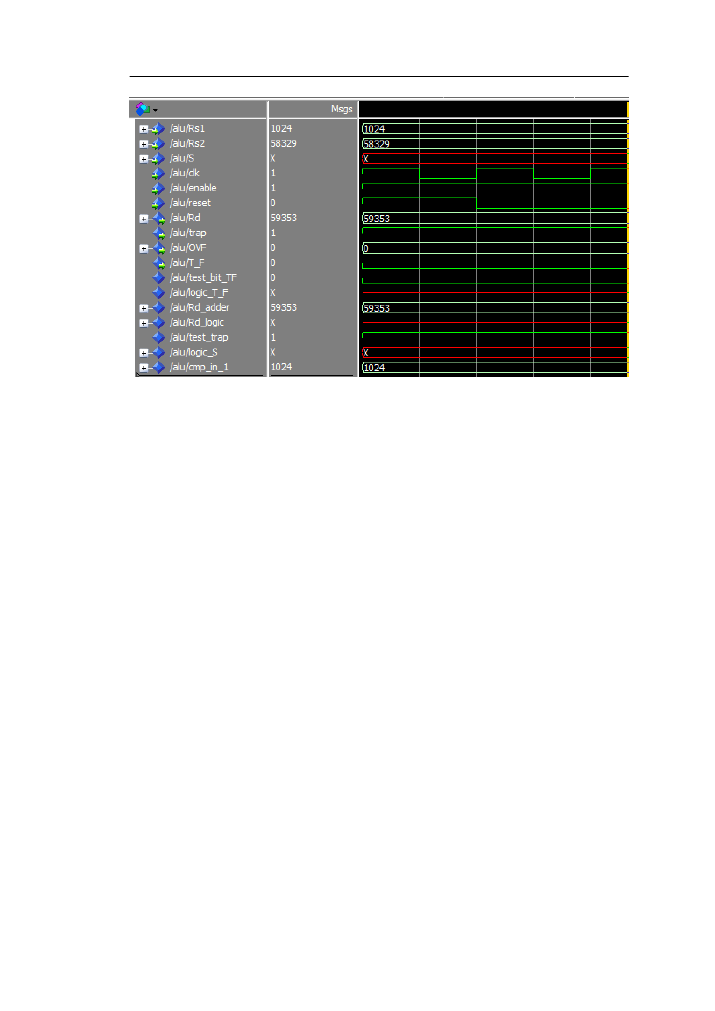

Figure 2.7: ALU simulating an addi operation

the next adder as well as the proper adders required when executing subword additions.

For example if the addition is performed between 4 32bit size words, the fourth adders’

carry out will be driven to the first adder and the 8th adder’s carry out will be driven to

the 5th adder as displayed in Figure

and

. This carry out propagation is required

only for the modular addition where the carry out is fed back to the carry in. The adder

can perform signed/unsigned and modular/non-modular additions/subtractions.

The comparator performs all the basic comparisons(equality, comparison, minimum,

maximum) between the two 64bit words as well as between all the subwords separately

depending on the instruction.

Figure

displays an example of the simulation of the ALU. Presenting here every

single instruction and subword combination is not possible, however all instructions have

been simulated and verified. Appendix D provides a full list with all the components,

including the ALU, and their signal encoding according to the instructions; refer to this

table to set the proper signals in the simulations.

2.5.2

The Multiplier

The multiplier performs all the basic multiplying instructions. It can perform signed or

unsigned multiplications between 16bit size words. These words can be either the odd