Chapter 2. The processor

35

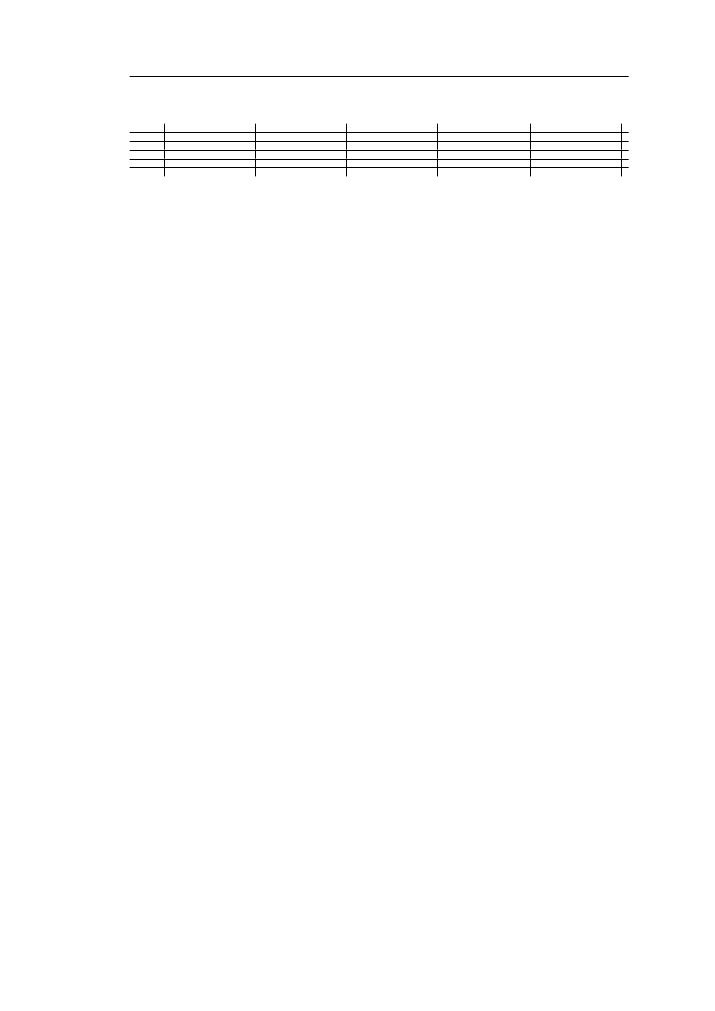

Table 2.14: Branch Hazard example

T1

T2

T3

T4

T5

stage 1

cmp.gt(PD2,PD3)

jmp(

PD2

,Rd)

stage 2

cmp.gt(

PD2

,PD3)

jmp(PD2,Rd)

stage 3

cmp.gt(PD2,PD3)

jmp(PD2,Rd)

stage 4

cmp.gt(,PD2,PD3)

jmp(PD2,Rd)

stage 5

cmp.gt(PD2,PD3)

that targets the same predicate that is used for the ”jump” instruction there is a po-

tential hazard in the execution as displayed in table

. The ”jump” instruction must

not be executed before the predicate file is updated.

2.10.3

Structural Hazards

structural hazard occurs when a part of the processor’s hardware is needed by two or

more instructions at the same time. In this case this type of hazard can occur in the

register file and specifically if there is a read and write instruction targeting at the same

time the same register. However this type of hazard is dealt as mentioned earlier by

forcing the read and write instruction to access the register file at different clock edges.

2.10.4

Pipeline bubbling

There are several ways to deal with data hazards in the pipelined processors. Bubbling

or pipeline stall is the simplest solution. Pipeline stalling is a way of preventing data,

structural, and branch hazards from occurring. As instructions are fetched, control

logic determines whether a hazard could/will occur. If this is true, then the control

logic inserts NOPs into the pipeline. Thus, before the next instruction (which would

cause the hazard) is executed, the previous one will have had sufficient time to complete

and prevent the hazard.

This method being the simplest is extensively used in the processor. Specifically it is

used for all the multicycle instructions such as the subtraction which requires two cycles

to complete. A more efficient way of dealing with the multicycle instructions would be

to modify the processor to a superscalar one, where there would be multiple instances

of the processing units, such as the ALU. While one component is busy calculating, the

other unit can be utilised for another instruction. However since area constraints is a

major factor the pipeline solution was chosen.