Chapter 2. The processor

32

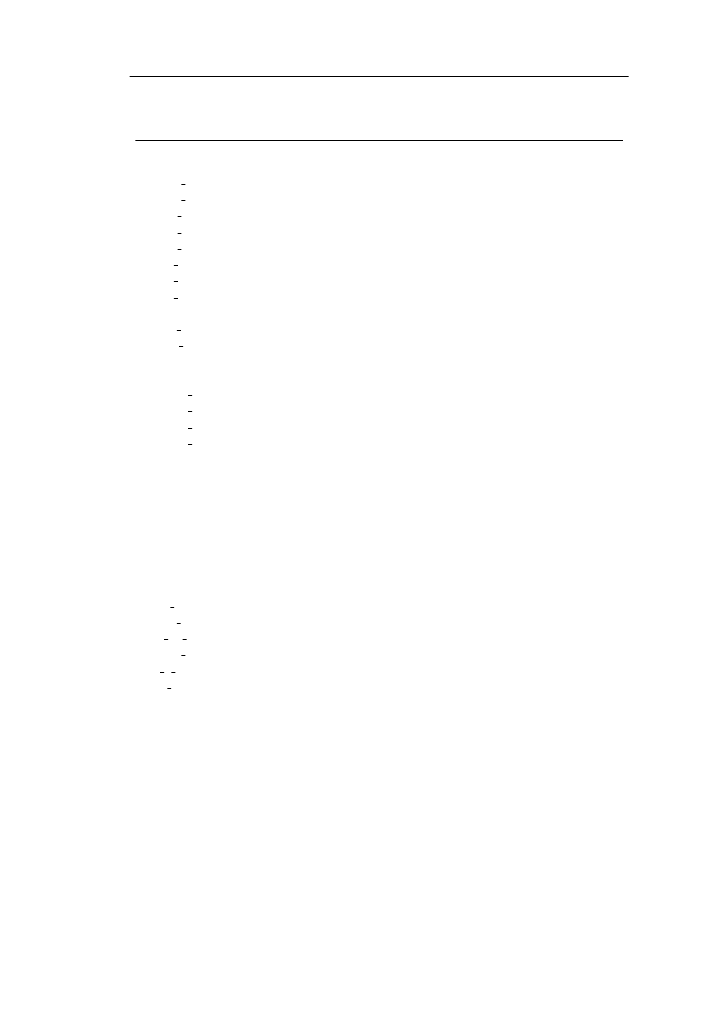

Table 2.11: The Control Unit ports

Name

Type

Size

Explanation

op

input signal

16

The operation to be executed

subop

input signal

3

Sub-operation(required for some instructions)

Rs1A st2

input signal

5

Rs1 stage 2 address

Rs2A st2

input signal

5

Rs1 stage 2 address

Rda st3

input signal

5

Rd stage 3 address

Rda st4

input signal

5

Rd stage 4 address

Rda st5

input signal

5

Rd stage 5 address

Pd st3

input signal

1

predicate signal from stage 3

Pd st4

input signal

1

predicate signal from stage 4

Pd st5

input signal

1

predicate signal from stage 5

trap

input signal

1

trap signal from ALU

ALu OU

input signal

8

Overflow/Underflow signal from ALU

ALU TF

input signal

1

True/False signal from ALU

clk

input signal

1

clock signal

reset

input signal

1

reset signal

controls st1

output signal

2

Stage 1 control signals

controls st3

output signal

51

Stage 3 control signals

controls st4

output signal

8

Stage 4 control signals

controls st5

output signal

6

Stage 5 control signals

mux1

output signal

2

M1 control signals

mux2

output signal

1

M2 control signals

mux3

output signal

3

M3 control signals

mux4

output signal

3

M4 control signals

mux5

output signal

2

M5 control signals

mux6

output signal

1

M6 control signals

mux7

output signal

3

M7 control signals

mux8

output signal

1

M8 control signals

mux9

output signal

1

M9 control signals

PC Stall

output signal

1

program counter stall signal

trap out

output signal

1

illegal trap flag

alu ou out

output signal

8

overflow/underflow flag

illegal out

output signal

1

illegal instruction flag

st 1 flush

output signal

1

stage 1 flush instruction

G stall

output signal

1

global stall signal

2.8.3

The Flag Unit

The flag unit is responsible for handling and sending the proper flag signals when an

error occurs. The way they are handled is by sending an output signal from the processor

top module for one clock cycle on the cycle that the error was detected. This means that

an external unit for proper handling and storing these flag signals is required. Table

shows the ports used by the module. The illegal flag is raised when an instruction

that is not encoded is requested. The trap flag is raised when when the instruction