Chapter 2. The processor

31

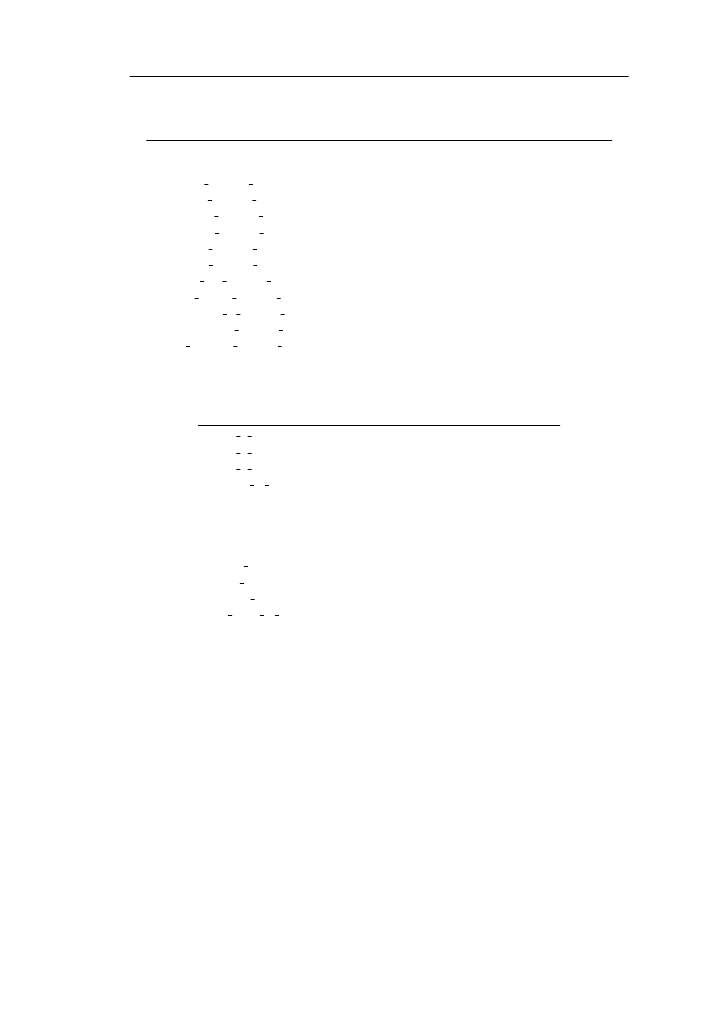

Table 2.9: The OP Decoder Unit ports

Name

Type

Size

Explanation

op

input signal

16

operation signals

subop

input signal

3

sub-operation signals

PC control signals

output signal

2

program counter signals

ALu control signals

output signal

20

ALU signals

MULT control signals

output signal

8

multiplier signals

SHIFT control signals

output signal

9

shifter

MIX control signals

output signal

6

MIX signals

FPU control signals

output signal

4

FPU signals

SIGN ext control signals

output signal

1

sign extension signals

DATA MEM control signals

output signal

8

data memory signals

REGISTER F control signals

output signal

2

register file signals

PREDICATE control signals

output signal

3

predicate file signals

REG INPUT control signals

output signal

4

register input signals

illegal

output signal

1

illegal operation flag

Table 2.10: The Stall Unit ports

Name

Type

Size

Explanation

st 1 op

input signal

6

stage 1 operation

st 2 op

input signal

6

stage 2 operation

st 3 op

input signal

6

stage 3 operation

subop st 3

input signal

6

stage 3 sub-operation

clk

input signal

1

clock signal

reset

input signal

1

reset signal

trap

input signal

1

trap signal

illegal

input signal

1

illegal flag input

FPU done

input signal

1

FPU done signal

PC Stall

output signal

1

PC stall

Global stall

output signal

1

Global stall

Reg flush st 1

output signal

1

register flush stage 1

2.8.2

The stall unit

This unit is responsible for stalling the processor when necessary in order to avoid

hazards. Stalling is enabled in multi-cycle operations, jump instructions and load in-

structions. There are two kinds of stalling implemented. The first is the global stall

where all the stages of the processor halt execution indefinitely and the second is the

PC stall where the program counter is stalled and a NOP instruction is inserted in the

pipeline. The stall unit is aware at any given time of the operations executed in stage 1,

stage 2 and stage 3 of the processor so as to assess the situation and stall if necessary.

Table

displays the port list used by the module.