Chapter 2. The processor

16

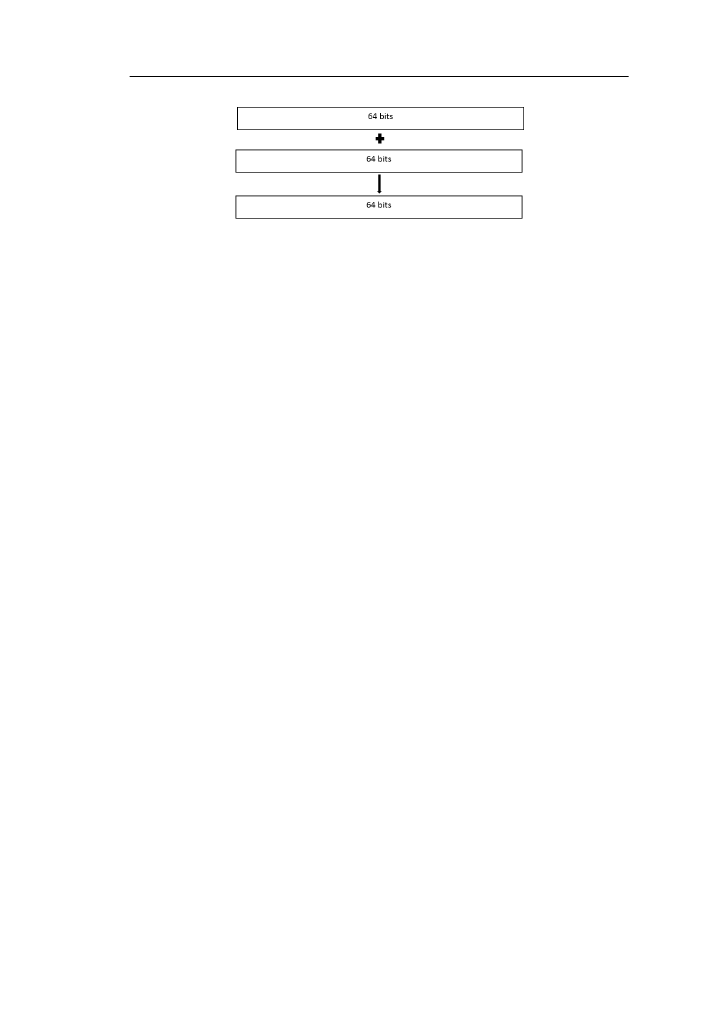

Figure 2.1: Addition between the whole 64bit words

2.1.1

Datapath Size

The datapath size chosen for the soft processor is 64 bits wide. The ISA itself supports

32, 64 and 128 bits datapaths, however the 64 bit wide is the silver lining among the

other two[

]. Another feature that led to the decision of the 64bit wide datapath is

the fact that the FPU implementation described at chapter 3 is a double precision one,

hence the 64 bits. This is yet another example of the flexibility that is offered by soft

core implementations; designers are free to choose the datapath and experiment with

various sizes and make the best decision for their design. Smaller datapath reduces

consumption and cost, while larger datapaths increase the performance. Register R0

is hardwired to 0 meaning that no changes can be made to this register and the value

returned when requested will always be zero. R31 is the designated jump register used

for the jump instructions.

2.1.2

Subword Parallelism

The key characteristic of the processor is the subword parallelism support. This means

that certain instructions can be executed simultaneously to all the subwords of the 64bit

word. The subword size can be chosen by the program and is 8, 16, 32 or 64 bit long.

For example when executing the addition instruction between two words a choice can

be made so as to add the two 64 bit words or add separately their subwords as displayed

in figures

. Subword parallelism can increase the speed by up to 8 times

depending on the word size chosen. However it is evident that there is a significand loss

in precision when using the parallel instructions, but multimedia processing has a large

margin for these kinds of precision losses.