Chapter 4. The Processor Customization

52

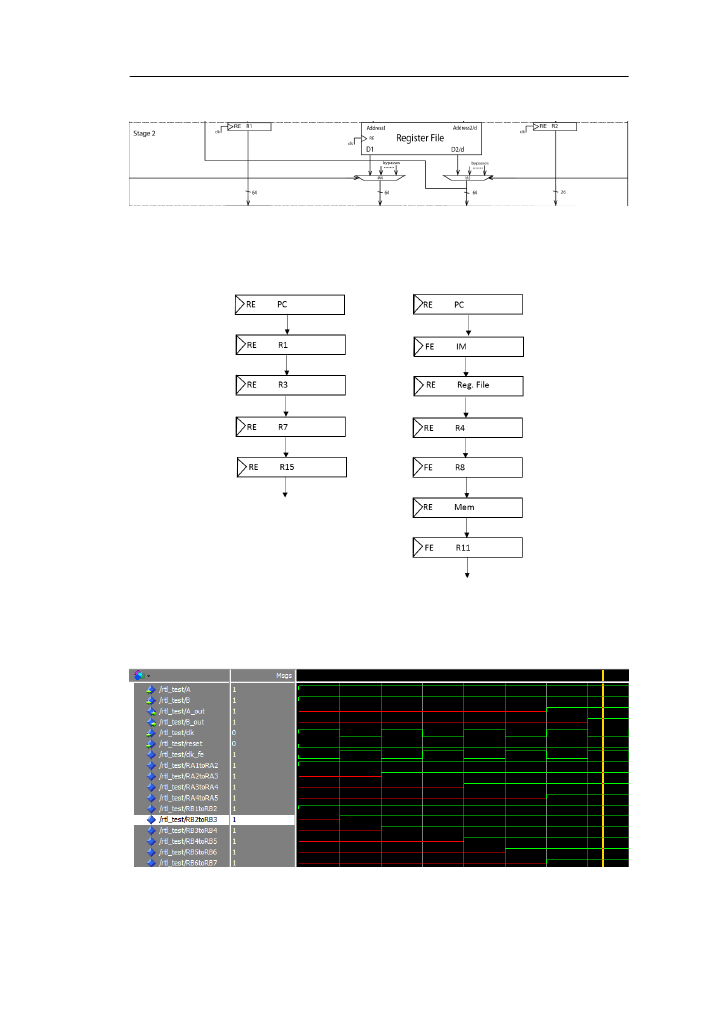

Figure 4.2: Stage 2 of the pipeline

Figure 4.3: Mirror RTL schematic for data propagation

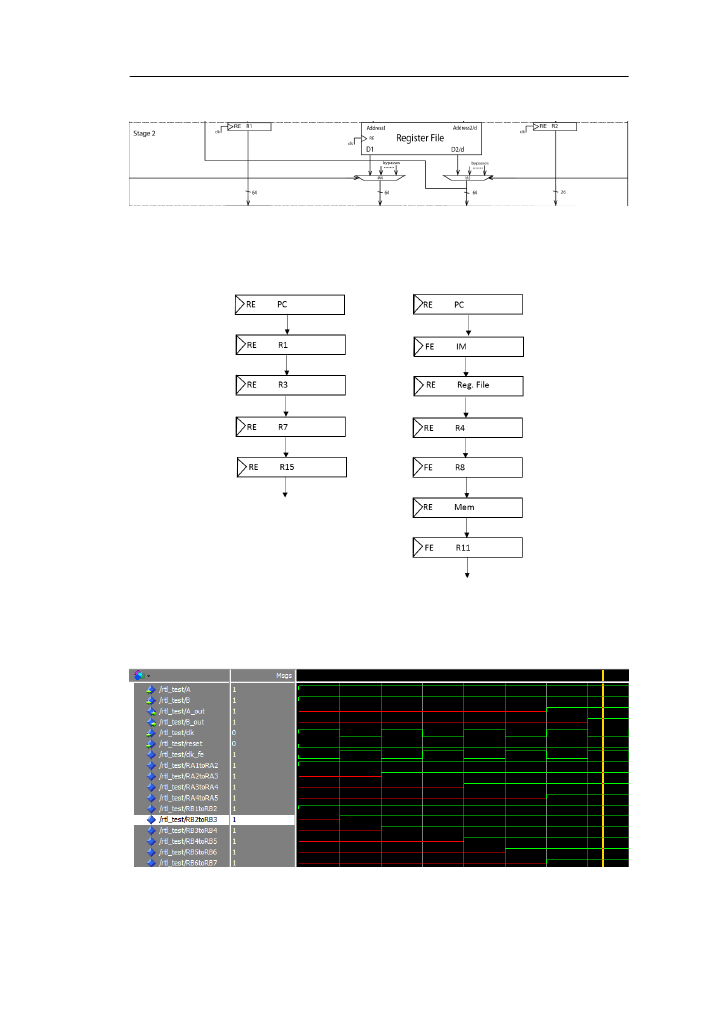

Figure 4.4: Mirror RTL simulation

Chapter 4. The Processor Customization

52

Figure 4.2: Stage 2 of the pipeline

Figure 4.3: Mirror RTL schematic for data propagation

Figure 4.4: Mirror RTL simulation