Chapter 3. The FPU

47

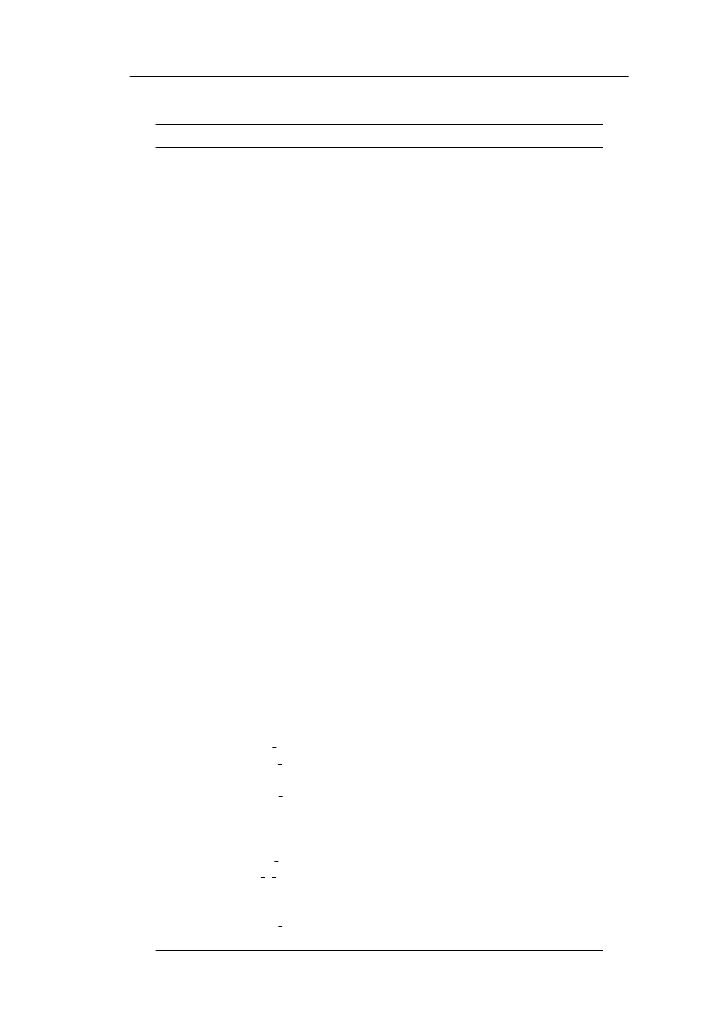

Table 3.4: Detailed device utilization summary for FPU

Slice Logic Utilization

Used

Available

Utilization

Number of Slice Registers

447

93,120

1%

Number used as Flip Flops

392

Number used as Latches

54

Number used as Latch-thrus

0

Number used as AND/OR logics

1

Number of Slice LUTs

2,223

46,560

4%

Number used as logic

2,215

46,560

4%

Number using O6 output only

1,807

Number using O5 output only

50

Number using O5 and O6

358

Number used as ROM

0

Number used as Memory

0

16,720

0%

Number used exclusively as route-thrus

8

Number with same-slice register load

5

Number with same-slice carry load

3

Number with other load

0

Number of occupied Slices

650

11,640

5%

Number of LUT Flip Flop pairs used

2,262

Number with an unused Flip Flop

1,875

2,262

82%

Number with an unused LUT

39

2,262

1%

Number of fully used LUT-FF pairs

348

2,262

15%

Number of unique control sets

7

Number of bonded IOBs

201

240

83%

Number of RAMB36E1/FIFO36E1s

0

156

0%

Number of RAMB18E1/FIFO18E1s

0

312

0%

Number of BUFG/BUFGCTRLs

2

32

6%

Number used as BUFGs

2

Number used as BUFGCTRLs

0

Number of ILOGICE1/ISERDESE1s

0

360

0%

Number of OLOGICE1/OSERDESE1s

0

360

0%

Number of BSCANs

0

4

0%

Number of BUFHCEs

0

72

0%

Number of BUFIODQSs

0

36

0%

Number of BUFRs

0

18

0%

Number of CAPTUREs

0

1

0%

Number of DSP48E1s

15

288

5%

Number of EFUSE USRs

0

1

0%

Number of FRAME ECCs

0

1

0%

Number of GTXE1s

0

8

0%

Number of IBUFDS GTXE1s

0

6

0%

Number of ICAPs

0

2

0%

Number of IDELAYCTRLs

0

9

0%

Number of IODELAYE1s

0

360

0%

Number of MMCM ADVs

0

6

0%

Number of PCIE 2 0s

0

1

0%

Number of STARTUPs

1

1

100%

Number of SYSMONs

0

1

0%

Number of TEMAC SINGLEs

0

4

0%

Average Fanout of Non-Clock Nets

3.58